据外媒报道,瑞萨电子推出了全新AI加速器,可高速且低功耗地执行CNN(卷积神经网络)处理,向下一代瑞萨嵌入式人工智能(e-AI)迈进,加速端点设备智能化。采用该加速器的测试芯片效率达到业界最高水平8.8 TOPS/W。瑞萨加速器基于计算存储一体化(PIM)架构,即当读取存储器数据时,在存储器电路中执行乘法和累加运算。

瑞萨开发人工智能加速器测试芯片

为构建全新AI加速器,瑞萨推出了以下三种技术。一是可执行大规模CNN计算的三进制(-1,0,1)SRAM结构PIM技术。二是与比较器配合使用的SRAM电路,可在低功耗下读取存储器数据。三是能够防止在制造过程中因工艺变化而导致的计算错误。将以上技术结合,既能缩短深度学习处理中的存储器访问时间,又可降低乘法和累加运算所需的功率。因此,当通过手写字符识别测试(MNIST)进行评估时,新加速器在保持99%以上准确率的同时,达到了业界最高能效等级。

由于二进制(0,1)SRAM结构只能处理值为0或1的数据,PIM架构无法通过单比特计算获得足够的大规模CNN运算精度水平。此外,制造过程中的工艺变化导致这些运算的可靠性降低。针对这些问题,瑞萨现已开发出攻克这些问题的三大技术,并将其作为实现未来革命性AI芯片的前沿技术应用于下一代e-AI解决方案,例如对性能和功率效率有较高要求的可穿戴设备及机器人等。

技术一:可根据所需精度调整计算位数的三进制(-1,0,1)SRAM结构PIM技术

三进制(-1,0,1)SRAM结构PIM技术采用三元存储器与简单数字计算块相组合,保证硬件数量增加的同时将计算误差降至最低。同时,允许根据所需精度进行位数切换(如1.5位(三进制)和4位计算之间)。可针对不同用户需求支持不同的精度及运算规模,用户可优化精度与功耗间的平衡。

技术二:结合比较器和复制单元的高精度/低功耗存储器数据读取电路

当采用PIM架构时,通过检测SRAM结构中的位线电流值以读取存储器数据。尽管使用A/D转换器进行高精度位线电流检测是有效的,但这种方法功耗高且芯片面积较大。因此,瑞萨将比较器(1位感测放大器)与复制单元相结合,方便灵活控制电流,从而开发出高精度的存储器数据读取电路。此外,由于神经网络操作所激活节点(神经元)数量非常少(约1%),通过关闭未激活节点(神经元)读取电路以实现更低的运行功率。

技术三:消除制造过程中因工艺变化导致计算误差的规避技术

由于制造过程中的工艺变化,导致SRAM结构中位线电流值产生误差,从而造成存储器读取数据时出现错误。为解决这个问题,瑞萨在芯片内部覆盖了多个SRAM计算电路模块,由制造工艺变化最小的模块执行计算任务。由于激活节点只是所有节点中的一小部分,因此激活节点被有选择地分配给制造过程变化最小的SRAM计算电路模块执行计算。从而将计算误差降至几乎可忽略的水平。

瑞萨电子的e-AI方案

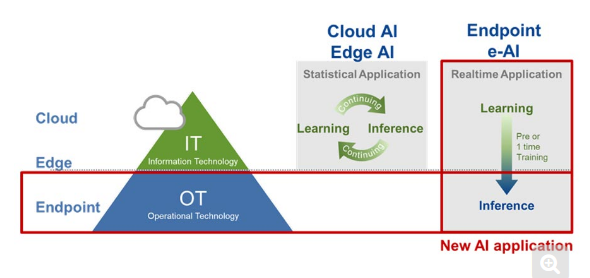

自2015年引入嵌入式AI(e-AI)概念以来,瑞萨一直致力于多个e-AI解决方案的研发。自2015年引入嵌入式AI(e-AI)概念以来,瑞萨一直致力于多个e-AI解决方案的研发。凭借灵活可扩展的嵌入式人工智能(e-AI)概念,瑞萨电子面向未来提供业界独一无二的实时低功耗人工智能处理解决方案,以满足端点嵌入式设备人工智能应用的特定需求。

瑞萨根据e-AI的有效性和已实施的应用程序定义了“类”,并根据以下四类开发出e-AI解决方案:

第1类:判断信号波形数据的正确性或异常。

第2类(100GOPS/W级):通过实时图像处理判断正确性或异常。

第3类(1TOPS/W级):实时识别。

第4类(10TOPS/W级):在端点启用增量学习。

瑞萨于2017年推出e-AI开发环境,并于2018年发布RZ/A2M微处理器,该微处理器集成瑞萨独有DRP技术,为第2类应用提供解决方案。同时,为实现第3类应用,瑞萨进一步提高了DRP技术的计算性能。

现在,瑞萨正立足此项开发并推出新型尖端技术。全新加速器技术结合低功耗特性和改进的计算性能,可能成为实现第4类应用的关键技术之一。瑞萨致力于通过在物联网边缘及端点采用AI技术来增强智能,为实现智能社会做出贡献。