1 引言

锁相环在通信、雷达、测量和自动化控制等领域应用极为广泛,已经成为各种电子设备中必不可少的基本部件。随着电子技术向数字化方向发展,需要采用数字方式实现信号的锁相处理。因此,对全数字锁相环的研究和应用得到了越来越多的关注。

传统的数字锁相环系统是希望通过采用具有低通特性的环路滤波器,获得稳定的振荡控制数据。对于高阶全数字锁相环,其数字滤波器常常采用基于DSP 的运算电路。这种结构的锁相环,当环路带宽很窄时,环路滤波器的实现将需要很大的电路量,这给专用集成电路的应用和片上系统SOC(system on chip)的设计带来一定困难。另一种类型的全数字锁相环是采用脉冲序列低通滤波计数电路作为环路滤波器,如随机徘徊序列滤波器、先N 后M 序列滤波器等。这些电路通过对鉴相模块产生的相位误差脉冲进行计数运算,获得可控振荡器模块的振荡控制参数。由于脉冲序列低通滤波计数方法是一个比较复杂的非线性处理过程,难以进行线性近似,因此,无法采用系统传递函数的分析方法确定锁相环的设计参数。不能实现对高阶数字锁相环性能指标的解藕控制和分析,无法满足较高的应用需求。

本文提出了一种基于比例积分(PI)控制算法的高阶全数字锁相环。给出了该锁相系统的具体结构,建立了系统数学模型,并对其系统性能进行了理论分析。采用MATLAB 软件对系统进行了仿真实验。应用EDA 技术设计了该锁相系统,并用

2 全数字锁相环的结构及工作原理

基于比例积分控制算法的三阶全数字锁相环的系统结构如图1 所示。该系统由数字鉴相器(DPD)、数字环路滤波器(DLF)和数控振荡器(DCO)三个部件组成。 图1 三阶全数字锁相环系统结构图

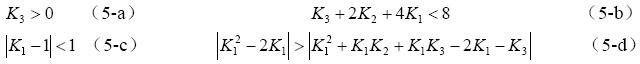

利用朱例(Jury)稳定判据,可以根据系统闭环特性方程的系数来判别特征根是否位于Z 平面的单位圆内,从而判别系统是否稳定。经分析推导可得,该三阶数字锁相环系统稳定的所有条件为:

fpga="" href="http://www.chinaaet.com/search/?q=<a class=" p="" style="text-decoration:underline;color:blue" title="FPGA ">

根据本系统在Z 域的传递函数和表2 中的设计参数K1 、K2 、K3 ,应用MATLAB 软件进行分析,得到三阶全数字锁相环在单位阶跃信号作用下的系统仿真曲线如图3 所示。