摘 要: 介绍了传统模拟Costas环路存在的问题,通过对Costas环路原理的分析,利用连续时间域与离散时间域之间的变换关系,推导出Costas环路的离散模型,据此阐述了环路各模块参数的计算及电路设计。最后利用FPGA对Costas环载波恢复电路进行了实现,并给出了所实现的RTL原理图。

关键词: Costas环 载波恢复 FPGA

Costas环路作为一种通用的BPSK载波恢复方法,其实质是一个负反馈电路,从而决定了它具有使本地载波的相位或频率与信号载波保持一致的能力。Costas环有许多优良的特性,如:载波跟踪特性、调制跟踪特性等[1]。但是传统模拟Costas环路因为存在同相支路和正交支路不平衡性及不可避免的零点漂移,均使环路的性能受到影响,同时模拟的Costas环路调试困难,而采用全数字的实现方式可以很好地解决以上问题。

1 二阶Costas环的连续域模型

图1所示为一个二阶Costas环路。其中输入信号为:

式中kd为鉴相器的灵敏度。

既然是恢复本地载波,必然要使VCO输出波形的相位同发送端波形的相位一致。由此可以建立整个环路方程[2]:

式中:k0是VCO的灵敏度,p是微分算子,F(p)是环路滤波器" title="环路滤波器">环路滤波器(LF)的传输算子。

因为在经过几个周期之后,θe将会变得很小,即有:

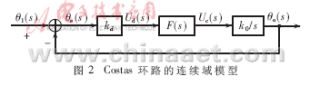

由此可知Costas环的连续域模型如图2所示。

为了达到较好的稳态误差及动态响应,环路滤波器一般采用有源RC积分滤波器,其传递函数" title="传递函数">传递函数为:

通过引入环路固有频率ωn和阻尼系数ξ,环路的开环传递函数可以表示为:

2 二阶Costas环的离散域模型

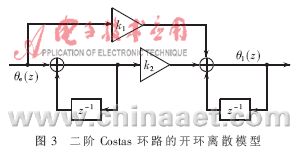

利用后向差分法可以将连续时间域的数学模型变换为稳定的离散时间域模型,即用 代替开环传递函数中的s,可以得到离散的开环传递函数:

代替开环传递函数中的s,可以得到离散的开环传递函数:

二阶Costas环路的开环离散模型如图3所示。

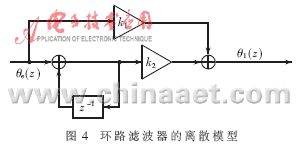

因为VCO的离散形式就是数控振荡器(NCO),其数学模型为 ,所以可以推导出环路滤波器的离散传递函数为:

,所以可以推导出环路滤波器的离散传递函数为:

环路滤波器的数学模型如图4所示,据此可以对环路滤波器进行设计。

3 Costas环路的设计与仿真" title="设计与仿真">设计与仿真

设计中系统时钟为48MHz,作为NCO、LPF的控制时钟。载波频率为240kHz,在一个周期内采样20个点,所以采样时钟为4.8MHz,同时也作为乘法器" title="乘法器">乘法器的时钟。本文所有的设计都是基于Xilinx ISE7.1i的集成开发环境与ModelSim6.1b仿真软件。

3.1 NCO的设计

数控振荡器采用直接数字频率合成DDFS(简称DDS技术)设计。DDS是从相位概念出发直接合成所需波形的一种新的频率合成技术[3]。一个直接数字频率合成器一般由一个相位累加器、ROM波形表组成。其中相位累加器由一个N位全加器和一个N位累加寄存器级联而成,对频率控制字" title="控制字">控制字的二进制码进行累加运算。在每个系统时钟沿fclk的控制下,N位加法器将频率控制字X与累加寄存器输出的相位数据相加,把相加后的结果再送至累加寄存器,累加寄存器中新的相位数据即反馈到加法器的输入端,以使加法器在下一个fclk时钟周期中继续与频率控制字X相加,同时累加寄存器的高M位数值将作为查找ROM表中取样数据的地址值。ROM查找表中储存着一个完整周期的正弦波幅度信息,通过取得的采样地址值进行查表,从ROM表中输出相应的波形采样数据fout。可以证明:

用VHDL对NCO进行设计时,可以分为三个子模块,第一个是频率控制字的载入模块,第二个是相位累加模块,第三个是查表模块。

3.2 乘法器设计与仿真

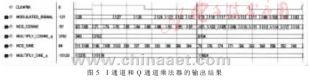

数字乘法器有各种实现方式,如Booth乘法器、Baugh-Wooley乘法器、串行并行乘法器等。各种实现算法的速度、资源占用情况都不一样[4]。此处直接调用了Xilinx公司的IP Core。该乘法器是一个有符号数乘法器,且是一级流水。对于本设计两个输入都是8位的,输出结果是16位。由于两个输入都是介于-1与+1之间的数,而在FPGA设计中采用整数定点运算,所以乘法器的最终输出应该除以128。图5是乘法器的仿真输出结果。

3.3 低通滤波器的设计与仿真

通过分析可知:低通滤波器应该将乘法器输出信号中480kHz的高频滤去。由于该FIR数字滤波器的阶数比较高,直接设计困难较大,所以利用Matlab中Simulink的FDAtool工具箱来设计。设计中的参数选择如下:fs=4.8MHz,fpass=48kHz,fstop=456kHz,低通段的增益为1db,截止段的增益为-40db。按以上参数设计完成后得到一个17阶的数字滤波器,其系数分别为:2、3、4、6、8、9、11、12、12、12、11、9、8、6、4、3、2,然后将这些系数下载到一个ROM存储器中。最终的仿真输出结果如图6所示,由图可知滤波效果非常好。

3.4 环路滤波器的设计

根据图4所示环路滤波器的离散模型,可以直接用VHDL进行描述。离散域内的IIR滤波器由一个带反馈的一级流水线的累加器和一个一级流水线的加法器组成。两个和系数相乘的乘法器将简化为数据寄存器的左移和右移,设计关键点是对k1、k2两个参数进行计算。考虑到整个环路的增益、量化、扩位以及进一步的计算,最终取k1=64,k2=2。具体推导见参考文献[5]。

图7是整个Costas环在FPGA上实现以后的顶层RTL原理图。

图8为载波跟踪的仿真输出。由图可见在经过有限个载波周期之后,本地恢复波形就与载波的相位对准,由于载波频率为240kHz,可以知道即使在经过240周期之后二者相位才对准,载波恢复的时间仍然能够达到1ms,所以具有很好的快速跟踪性能。

利用现代EDA技术将原先用分立元件实现的模拟Costas环集成在一块Xilinx Spartan-3 XC3S400 FPGA器件上面,不仅提高了系统的可靠性,而且由于FPGA自身的可重配置性,使得采用FPGA进行设计具有设计灵活性,用户可以在不改变外部设计的情况下,根据需要非常方便地改变Costas环路的跟踪频率带宽,随时优化、扩展电路的功能,系统整体柔性得到提高。

参考文献

[1] Roland E Best.Phase-Locked Loops Design,Simulation and Applications.北京:清华大学出版社,2003.

[2] 王福昌,鲁昆生.锁相技术.武汉:华中科技大学出版社,1997.

[3] MORELLI D.Modulating Direct Digital Synthesizer in a Quciklogic FPGA.http://www.ieechina.com

[4] 张欣.VLSI数字信号处理——设计与实现.北京:科学出版社,2003.

[5] 张欣.扩频通信数字基带信号处理算法及其VLSI实现.北京:科学出版社,2004.